Kapuáramkörök

A számítógép egy műszakilag megvalósított rendszer,⇒ amelynek a legfontosabb eleme a számítógép központi egysége, ezen belül a központi feldolgozó egysége (CPU), amely a számítógép programozott működését hardver szinten megvalósítja, ill. vezérli (metaforikusan kifejezve a működés alapvető "logikáját" szolgáltatja).

A CPU működésének elvi szintű megértéséhez az első lépés azoknak az alapáramköröknek, ún. kapuáramköröknek a megismerése, amelyekből komplex logikai hálózatokat tudunk felépíteni. Ezek a hálózatok teszik lehetővé, hogy a CPU képes legyen a számítógép működése szempontjából alapvető feladatok elvégzésére (például az éppen futó program utasításainak beolvasására, az utasítások értelmezésére és végrehajtására, a megfelelő műveletek elvégzésére, szükség esetén a futó programok megszakítására stb.).

Összetett, komplex logikai függvényeket megvalósító rendszereknél (és a számítógépek túlnyomó többsége ilyen), "nem célszerű egyetlen, ugyancsak bonyolult logikai hálózatot tervezni. Előnyösebb, ha ilyenkor a bonyolult logikai feladatot több, de önmagukban viszonylag egyszerű logikai hálózat létrehozásával, azok összehangolt működtetésével oldjuk meg. A logikai hálózatoknak az így kialakuló rendszere alapján bevezethetjük a logikai rendszer fogalmát." (Arató 1996: 18)Egy logikai rendszerben az egyes részfeladatokat végző funkcionális egységek vezérlését egy ún. vezérlő egységgel kell biztosítanunk. A vezérlő egységet megvalósíthatjuk például egy olyan logikai hálózattal, amely a megfelelő vezérlő jelek kiadásával hangolja össze és ütemezi a funkcionális egységek működését:

(1) A vezérlő jeleket a vezérlő egység meghatározott logikai feltételek teljesülése esetén adja ki; a logikai feltételeket meghatározó logikai értékek származhatnak

○ az (egy vagy többfázisú) órajelgenerátor által kiadott órajelekből,

○ más funkcionális egységek vagy áramkörök által kiadott vezérlő jelekből (például egy kétállapotú gomb kimenetéből, a megszakításvezérlő egység kimeneteiből stb.),

○ a vezérlő egység, ill. a funkcionális egységek belső állapotát tároló regiszterekből (például az állapotregiszterből, a megszakításregiszterből, a fázisregiszterből stb.),

○ stb.

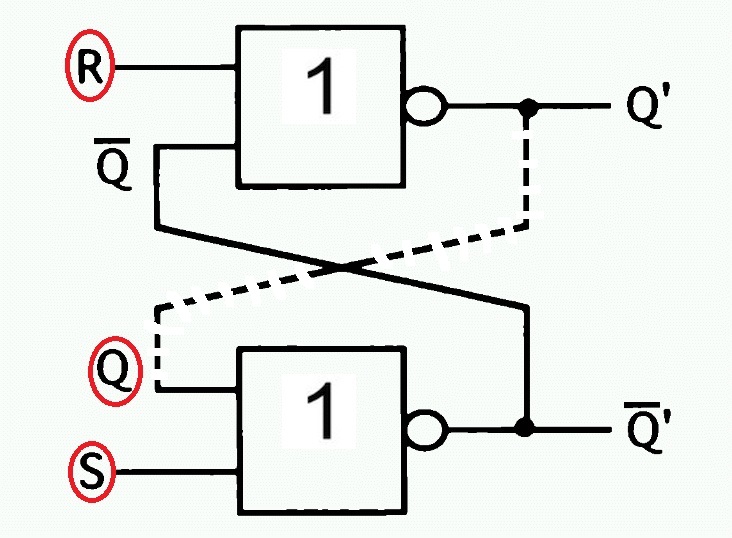

(2) A vezérlő egység által kiadott vezérlő jelek végzik a funkcionális egységek vezérlését (például szinkron sorrendi hálózatok esetén az órajelek engedélyezik vagy tiltják azoknak a tároló áramköröknek ("flip-flopoknak") a működését, amelyek a bemeneteket, a belső állapotokat, a kimeneteket stb. tárolják).Egy logikai hálózat vagy egy logikai rendszer funkcionális egységeinek működését meghatározott vezérlő jelek segítségével vezérelhetjük. (Ilyenek lehetnek például az órajelek, a vezérlő egység kimenetei stb.)A logikai alapáramkörök vagy kapuáramkörök⇒ és a logikai hálózatok⇒ működési elveinek megismerése után még visszatérünk a logikai rendszerek vezérlésének⇒ kérdésére.

Függetlenül technikai megvalósításuktól, a kapuáramkörök olyan fekete dobozoknak tekinthetőek, amelyekben az inputot és az outputot jelentő feszültségjelek a logikai 0 és 1 állapotoknak felelnek meg. Ebben az értelemben egy kapuáramkör egy adott logikai műveletet reprezentál. A kapuáramkör bemenetét az adott logikai művelet független változóinak lehetséges értékei ("kombinációi") adják, a kapuáramkör kimenete pedig az adott logikai művelet eredménye lesz.

A kapuáramkörök, valamint a bemenetükön, ill. kimenetükön megjelenő bináris jelek szemléltethetőek olyan áramkörök ("kapcsolások") segítségével, amelyek csak telepeket, mechanikus kapcsolókat és izzólámpákat tartalmaznak (vö. pl. Urbán 1987: 14-22). Érdemes megjegyeznünk, hogy ha mechanikus kapcsolók helyett elektromechanikus, kivülről elektromos jelekkel vezérelhető kapcsolókat (jelfogókat vagy reléket) használunk, akkor nemcsak a kapuáramkörök, hanem összetett logikai hálózatok is kialakíthatók (elvileg akár egy programvezérelt számítógép is).

A kapuáramkörök tényleges kialakítása számos módon lehetséges. Korábban például telefonreléket, elektroncsöveket, diódákat ill. tranzisztorokat használtak. Ezek közül a tranzisztorok kiemelt jelentőségűek, mivel ezek képezik az alapját a napjainkban használt integrált áramköröknek. A mai számítógépekben nagy bonyolultságú (ún. VLSI) integrált áramkörökben, "chipekben" hozzák létre a kapuáramköröket és a belőlük kialakított összetett logikai hálózatokat.

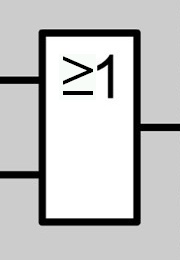

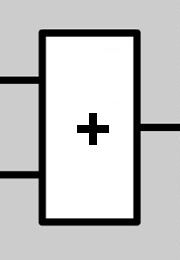

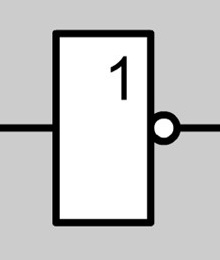

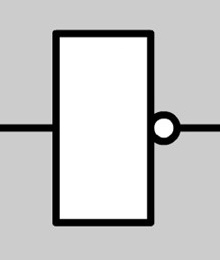

Tárgyalásunk szempontjából alapvető, hogy a logikai alapműveletek megvalósíthatók digitális áramkörök, ún. kapuáramkörök segítségével.A logikai alapműveleteket megvalósító kapuáramköröket például az alábbi szimbólumokkal ábrázolhatjuk:

Korábban láttuk, hogy a logikai alapműveletek segítségével minden logikai függvény kifejezhető. Ennek megfelelően a kapuáramkörök megfelelő összekapcsolásával tetszőleges logikai függvény műszakilag megvalósítható.

A kapuáramkörök összekapcsolásával létrehozott logikai hálózatok elvileg bármilyen logikai függvény műszaki megvalósítását lehetővé teszik.

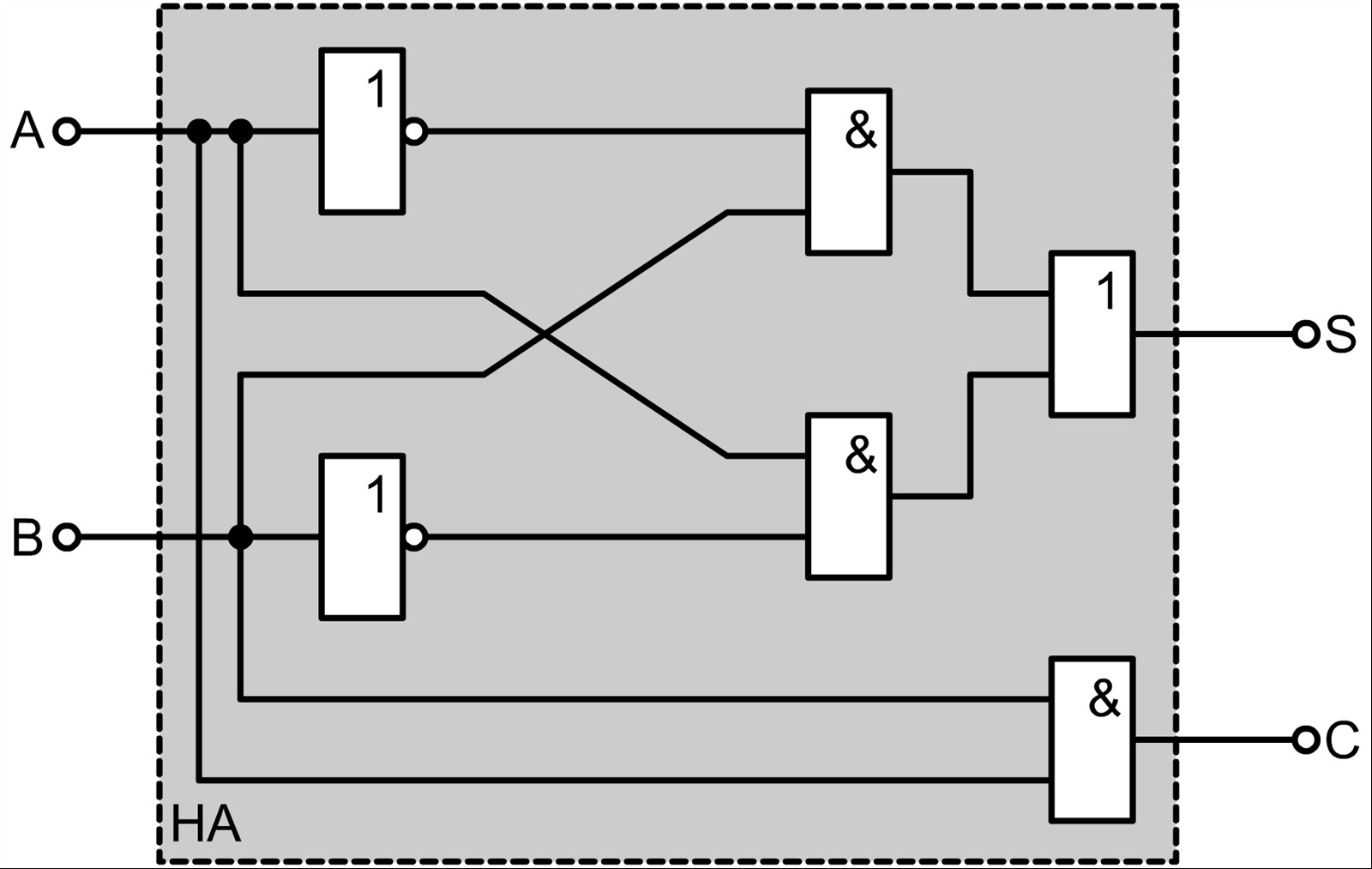

1. példa: egy egyszerű egybites összeadó, ún. félösszeadó áramkör igazságtáblázata és kapuáramkörökkel történő megvalósítása (HA, half adder; vö. Wikipédia, Sulinet Tudásbázis):

A fenti igazságtábla két egybites szám (A és B) összegét adja meg (S), valamint az összeadáskor fellépő maradékot (C). Az igazságtáblázat alapján a félösszeadót megvalósító logikai függvények t.d.n.f.⇒ alakja a következő:

S = ( ⌝A ∧ B ) ∨ ( A ∧ ⌝B ) = A⨁B és

C = ( A ∧ B )Figyeljük meg, hogy a félösszeadó kapuáramkörökkel történő megvalósítása során

(1) a ⌝A és ⌝B jeleket egy-egy NOT kapuval állítjuk elő,

(2) a három AND kapu bemeneteit vagy közvetlenül a félösszeadó valamelyik bemenetéről (A és B), vagy valamelyik NOT kapu kimenetéről (⌝A és ⌝B) állítjuk elő,

(3) az összeget (S) egy OR kapu állítja elő, amelynek a bemenetét két AND kapu kimenete szolgáltatja, és

(4) az átvitelt a magasabb helyi értékek felé (C) egy AND kapu állítja elő, amelynek a bemenetét közvetlenül a félösszeadó bemenetei (A és B) szolgáltatják.

A félösszeadó működésének ismeretében felépíthető egy több bites bináris összeadó (ún. teljes összeadó). Ha a félösszeadó igazságtáblázatát egy oszloppal kibővítjük, amely az előző helyi értékről származó átvitelt (Ci vagy cin) tartalmazza, az ún. egybites teljes összeadó igazságtáblázatát⇒ kapjuk:

Az egybites teljes összeadó igazságtáblázatában

- A és B az összeadandó bitek,

- Ci (vagy cin) az előző helyi értékről átvitt (vagy átvett) bit (i=input),

- Co (vagy cout) a következő helyi értékre történő átvitel bitje (o=output),

- S az A és B megfelelő bitjeinek összege, pontosabban ennek legalacsonyabb helyiértékű bitje.

Feladat:

Valósítsuk meg az igazságtábla alapján az egybites teljes összeadót (FA, Full Adder). Az összeadás megszokott algoritmusát alkalmazva a feladat két félösszeadóval (HA, Half Adder) könnyen megoldható:Az ábrán szereplő teljes összeadót megvalósító logikai áramkört az alábbi logikai függvények írják le:

Stmp=(A∧⌝B)∨(⌝A∧B)

Ctmp=A∧B

S=(C∧⌝Stmp)∨(⌝C∧Stmp)

Csec=Stmp∧C

Cout=Csec∨CtmpMivel

⌝Stmp= ⌝(A∧⌝B)∧⌝(⌝A∧B)=

(⌝A∨B)∧(A∨⌝B)= (→ disztributivitás összetett formája⇒)

(⌝A∧A)∨(⌝A∧⌝B)∨(B∧A)∨(⌝B∧⌝B)=

(⌝A∧⌝B)∨(B∧A)

Ezért

S=(C∧⌝Stmp)∨(⌝C∧Stmp)=

S=[C∧((⌝A∧⌝B)∨(B∧A))]∨ [⌝C∧((A∧⌝B)∨(⌝A∧B))]=

S=(C∧⌝A∧⌝B)∨(C∧B∧A)∨ (⌝C∧A∧⌝B)∨(⌝C∧⌝A∧B)=

S=(A∧⌝B∧⌝C)∨(⌝A∧B∧⌝C)∨ (⌝A∧⌝B∧C)∨(A∧B∧C)Másrészt

Csec=Stmp∧C=

[(A∧⌝B)∨(⌝A∧B)]∧C=

(A∧⌝B∧C)∨(⌝A∧B∧C)

Tehát

Cout=Csec∨Ctmp=

[(A∧⌝B∧C)∨(⌝A∧B∧C)]∨(A∧B)=

(A∧⌝B∧C) ∨ (⌝A∧B∧C) ∨ [(A∧B) ∨ (A∧B∧C)] = (→ abszorpció összetett formája⇒)

[(A∧⌝B∧C) ∨ (A∧B∧C)] ∨ [(⌝A∧B∧C) ∨ (A∧B∧C)] ∨ (A∧B) =

(A∧C)∨(B∧C)∨(A∧B) =

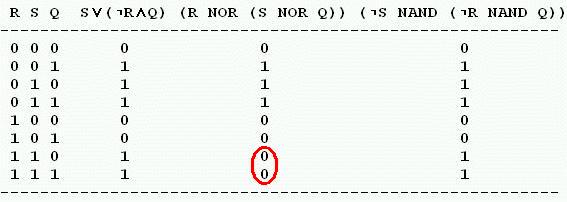

(A∧B)∨(A∧C)∨(B∧C)Ellenőrizzük a teljes összeadót megvalósító logikai áramkör működését egy igazságtáblázattal:

egybites teljes összeadó igazságtáblázata A B C=Cin Stmp Ctmp S Csec Cout 0 0 0 0 0 0 0 0 0 1 0 1 0 1 0 0 1 0 0 1 0 1 0 0 1 1 0 0 1 0 0 1 0 0 1 0 0 1 0 0 0 1 1 1 0 0 1 1 1 0 1 1 0 0 1 1 1 1 1 0 1 1 0 1 Ellenőrzésként vessük össze a táblázat első három oszlopának, valamint a pirossal és sárgával kijelölt oszlopoknak az értékeit az egybites teljes összeadó korábban elkészített igazságtáblázatával.⇒

Az egybites teljes összeadó kimenetének leírása logikai függvényekkel (három logikai változóval, t.d.n.f. alakban⇒ ):

S(A,B,C) = (⌝A∧B∧⌝C) ∨ (A∧⌝B∧⌝C) ∨ (⌝A∧⌝B∧C) ∨ (A∧B∧C) = A⨁B⨁C

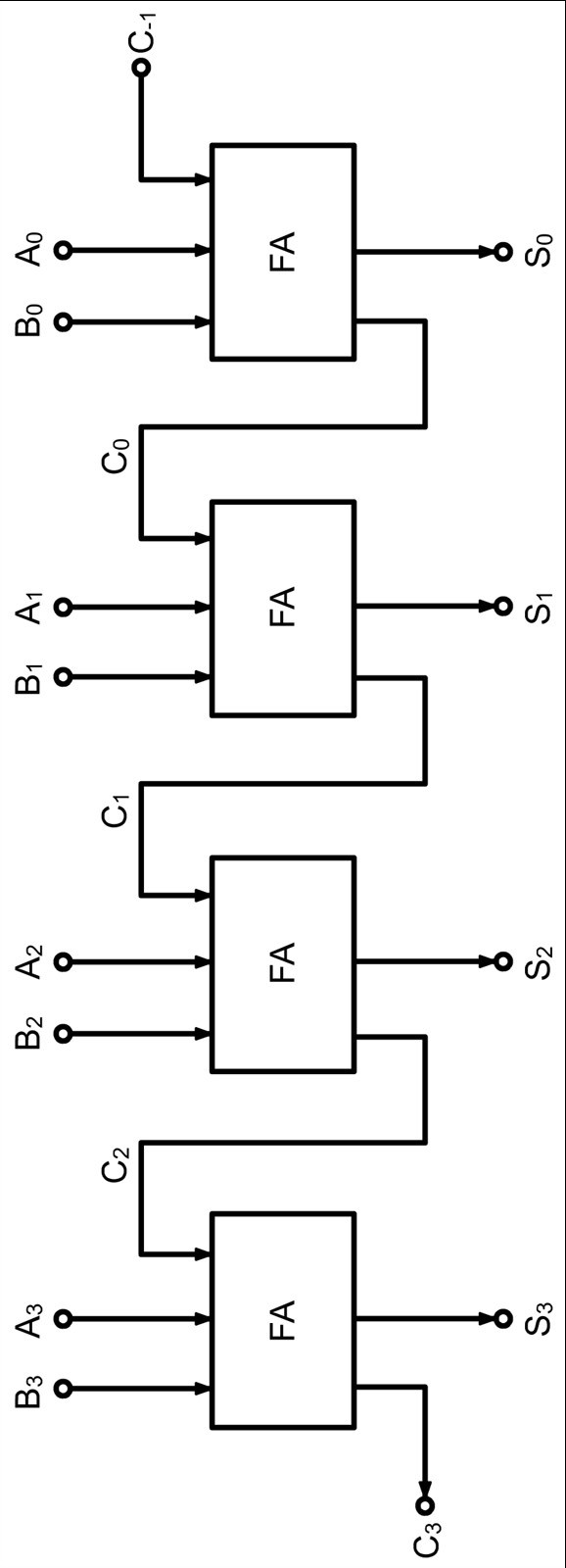

Cout(A,B,C) = (A∧B∧⌝C) ∨ (⌝A∧B∧C) ∨ (A∧⌝B∧C) ∨ (A∧B∧C) = (A∧B) ∨ (A∧C) ∨ (B∧C)Az egybites teljes összeadó áramkörök összekapcsolásával pedig könnyen megvalósíthatunk egy 'n' bites teljes összeadót. Például az alábbi ábrán egy 4 bites teljes összeadó látható (vö. Wikipédia, Sulinet Tudásbázis).

Vegyük észre, hogy a kép valamilyen oknál fogva nem a szokásos, balról jobbra történő jelterjedési irányt ábrázolja, hanem pont fordítva (azaz az álló helyzetben megjelenített ábra jobbról balra "olvasandó".)

Jegyezzük meg, hogy

- a legalacsonyabb helyi értéken nincs "bejövő" átvitel, tehát értelemszerűen C−1=0;

- a legmagasabb helyi értékű biten pedig az átvitel (C3=1) ún. túlcsordulást jelez.

A túlcsordulás rendszerint azt jelzi, hogy adott számú bit esetén az összeadás nem végezhető el, mivel a kapott összeg több bitből áll, mint a számok ábrázolására vagy tárolására rendelkezésre álló bitek száma. (Például 11012+10002=101012 esetén az összeadandók 4 bitesek, az összeg viszont 5 bites.)

Emeljük ki, hogy a példákban szereplő logikai hálózatok esetében

(1) a kimenet kizárólag a bemenetre adott jelektől függ, és

(2) ideális esetben feltételezzük, hogy a kimeneti jelek a bemeneti jelek hatására "azonnal" (azaz késleltetés nélkül) megjelennek.Az ilyen típusú hálózatokat kombinációs hálózatoknak nevezzük.

A kapuáramkörök felhasználásával interaktívan különböző logikai hálózatokat alakíthatunk ki az alábbi internetes címeken:

Logic Gate Simulator | Academo.org – Free, interactive, education.

https://academo.org/demos/logic-gate-simulator/ (2022-11-19)simulator.io - Build and simulate logic circuits.

https://simulator.io/ (2022-11-19)

2. példa: egy 2-4 dekóder bemenete egy két bites bináris szám két számjegye (bitje). A dekóder 22=4 kimenettel rendelkezik. A dekóder úgy működik, hogy a bemenet minden lehetséges értékkombinációja esetén a kimenetek közül mindig pontosan egy vesz fel 1 értéket, és különböző bemenetekhez különböző kimenetek tartoznak.

Az áramkör igazságtáblázata, és kapuáramkörökkel történő egy lehetséges megvalósítása a következő (vö. Wikipedia):

A fenti igazságtábla egy kétbites bináris szám számjegyeihez (A0 és A1) rendeli hozzá 2 nemnegatív egész kitevős hatványainak direkt kódban ábrázolt értékeit (ahol D0, D1, D3, D4 a direkt kódban ábrázolt szám számjegyei). Vegyük észre, hogy bármilyen 'A' input esetén a dekóder olyan 'D' outputot szolgáltat, hogy a D0, D1, D3, D4 számjegyek közül mindig pontosan egynek az értéke lesz 1 (a többi számjegy pedig zérus lesz).

Gyakorló feladatok

Hozzunk létre kombinációs hálózatokat, amelyek az alábbi logikai függvényeket valósítják meg ("realizálják"). Ahol lehet, próbáljuk meg egyszerűsíteni is a függvényeket! (vö. Fodor-Nagy 1982: 82-90):

(a) p(A,B)=(A∧⌝B) ∨ (⌝A∧B)

(b) p(A,B,C)=(A∧B∧⌝C) ∨ (A∧⌝B∧C) ∨ (A∧B∧C)

(c) p(A,B,C)=(A∧B) ∨ (⌝A∧B∧C) ∨ (⌝A∧B∧⌝C)

(d) p(A,B,C)=(A∧B) ∨ (⌝A∧⌝B) ∨ (A∧C)

(e) p(A,B,C)=(A∧B) ∨ (⌝A∧⌝B∧C) ∨ (⌝A∧B∧⌝C)

(f) p(A,B,C,D)=((A∧B∧C) ∨ ⌝B) ∧ ⌝D